In a computer system, an interrupt is a signal or event that prompts the operating system or a program to temporarily stop what it’s doing and switch its attention to handle a specific request or task that requires immediate attention. Interrupts are essential for the proper functioning of a computer system and help in managing multiple tasks efficiently.

What is Computer System Interrupt?

While the process is executed by the CPU and in between when a user requests for another process, this will create disturbance for the running process. This is known as the Interrupt.

CPU will handle all the interrupts carefully because the CPU provides responses to various Interrupts that are generated. When interrupts are generated, then the CPU will handle them with the help of fetch, decode, and execute operations.

Types of Interrupts

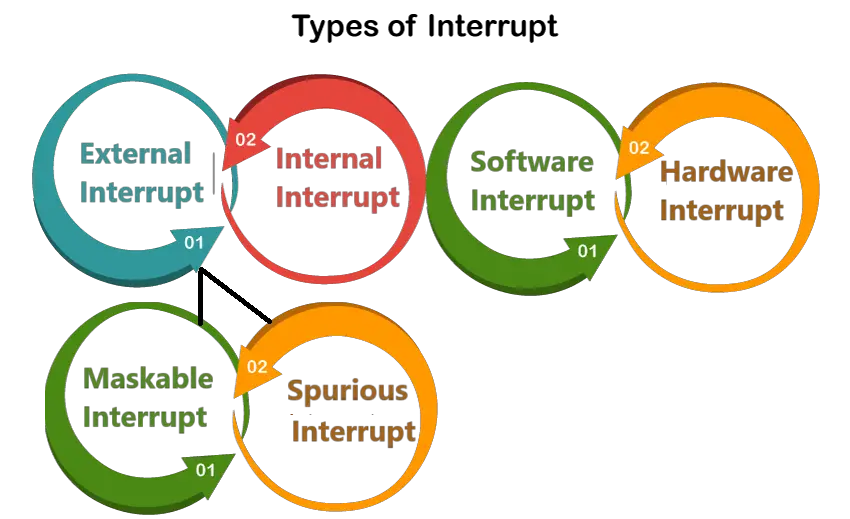

Generally, Interrupts are categorized into three types that include –

Internal Interrupt

The internal interrupt can be occurred when there is an issue in an execution. For example – when a user performing any operations that contains any error or any error type. Internal errors are those which are occurred by some operations or by some instructions and those are not possible however a user is trying to use it for an operation.

Software Interrupt

These are the interrupts which are made some call to the system. For example, while processing some instructions, if one wants to execute one more application program.

External Interrupt

This interrupt occurs when any input and output device request for any operation and the CPU will execute that instruction prior. For example, when a program is executing, when a mouse is moved on the screen, then the CPU will handle this interrupt first and later it will resume with the operation.

Further, the External Interrupts are divided into two sections-

Maskable interrupt

When the interrupt is disabled, the associated interrupt signal will be ignored by the processor. The signals that are affected that are affected by the mask are called maskable interrupts. However, the interrupt mask does not affect few interrupt signals and hence cannot be disabled are known as non-maskable interrupts (NMI).

These NMIs indicate high priority events which has to be proceed on an urgent basis and which cannot be ignored under any circumstances like timeout signal from a watchdog.

Spurious Interrupt

It is a hardware interrupt for which there is no source is found. Spurious interrupts may have concern with a wired or interrupt circuit attached to a level-sensitive processor input. Such interrupts are difficult to recognize when a system acts weird.

Why Interrupts are Required?

The external devices are slower when compared to CPU. Hence, if there is no interrupt, CPU might waste a lot of time waiting for external devices to match its speed with CPU. This however, decreases the efficiency of the CPU. Thus, interrupt needs to eliminate such limitations.

How to Use It?Â

- CPU instructs printer to print a specific document.

- While the printer does its tasks, CPU is engaged in executing other tasks.

- When printer is done with its work given, it communicates to CPU on the completion of the work.

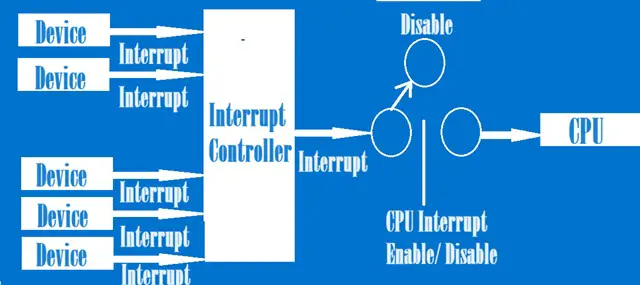

Handling Multiple Devices

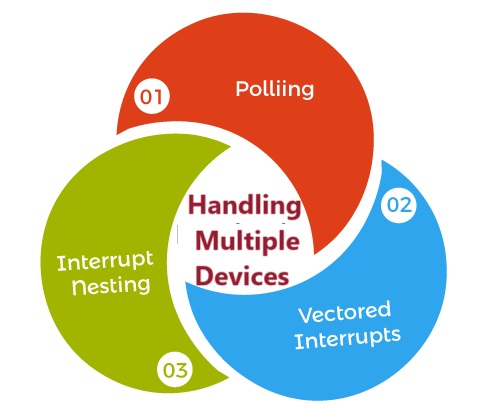

An additional information is required to decide which device to consider first when more than one device raises an interrupt signal. Below are the methods used to decide upon –

PollingÂ

In polling, the any device which comes across with IRQ bit is set to be considered first. This is easy to implement, however, while interrogating the IRQ bit of all devices, a lot of time is wasted.

Vectored Interrupts

Here, in vector interrupts, any device requests for interrupts can identify itself directly by sending a special code to the processor through the bus due to which the processor identifies the interrupted device which is generated. The special code can be the starting address of the ISR or the location where ISR is located in the memory and hence referred to as interrupt vector.

Interrupt Nesting

In interrupt nesting, the input and output device is recognized in a priority structure. Thus, any interrupt request from a higher priority device is recognized whereas the lower priority device is unrecognized. Any device or process which has much priority, the processor tends to accepts only those interrupts.

The processor’s priority is encoded in few bits of Process Status Register (PS) which later can be changed by program instructions that write into the process status register.

Handling

The instruction cycle consists of fetch, decode, execute and read/write functions. The processor will have a check for interrupts to be processed after every instruction cycle. In case, there is no interrupt in the system, it will proceed to next instruction cycle provided by the instruction register.

Suppose, the interrupt is present, then it will trigger the interrupt handler. The handler will stop the current instruction which is in the processing stage and saves it configuration in a register.

After the interrupt is processed by the processor, the interrupt handler will load the instruction and its configuration from the saved register. The process will start its processing from where its left.

There are two types of interrupt handlers that includes –

First Level Interrupt Handler (FLIH)

They are also termed as fast interrupt handler. They tend to panic more while execution of process and they are mainly maskable interrupts.

Second Level Interrupt Handler (SLIH)

It is soft and slow interrupt handler. These interrupts will may tend to panic less while execution of process.

The interrupt handlers are also called as interrupt service routine (ISR).

Features of Interrupt Service Routine

Below mentioned are some of the main features of Interrupt Service Routine –

- Interrupts can occur anytime and they remain same. The ISR’s can call for constant interrupts.

- An ISR’s can be called from various sources by an interrupt service mechanism.

- ISR’s has the ability to handle both maskable and non-maskable interrupts. Also, an instruction in a program can disable or enable an interrupt handler call.

- While at the beginning of the execution, the ISR will disable other devices interrupt devices. It will restart the interrupted services after the completion of the ISR execution.

- The nested interrupts are allowed in ISR for diversion to other ISR.

Difference Between Polling and Interrupts

The interrupts notify the controller that they need to be serviced when the flags or signals are received. Whereas, in Polling, the controller keeps monitoring the flags or signals one after the other for all the devices and provides service to which ever component needs to be serviced.

Steps for Executing the InterruptÂ

The microcontroller goes through the below steps while an interrupt gets active –

- The current execution process is closed by the microcontroller and it saves the address of the next instruction on the mound.

- It also saves the current status of all the interrupts internally.

- It moves to the memory location of the interrupt vector table which holds the address of the interrupts service routine.

- The microcontroller gets the addresses of the ISR from the vector table and moves into it. Later, it starts to execute the interrupt service subroutine which is return from interrupt (RETI).

- From the executing the return of interrupt instruction, the microcontroller returns to the location where it was interrupted. At first, it gets the program counter address from the mound by popping the top bytes of the mound into the PC and then it gets started for executing from that address.

Advantages

- Increase in efficiency of CPU.

- Decrease in waiting time of the CPU.

- It holds or stops the wastage of instruction cycle.

Disadvantages

- CPU has to do a lot of work in order to handle interrupts, resume its previous execution of programs.

Interrupts are an important part of the system because they provide the user better control over the computer without interrupt. A user might want to wait for the application that they are willing to use until it has a higher prior over the CPU to be ran. Thus, the use of interrupts lets the CPU to deal with the application required immediately.

Read Also: T FLIP FLOP – Construction/ Design, Working Principle and Applications Haptic Technology – Feedback, Devices, Working Principle, Applications

6d2pok

whoah this blog is magnificent i love reading your articles. Keep up the good work! You know, a lot of people are searching around for this info, you can aid them greatly.

Oh my goodness! an amazing article dude. Thank you Nevertheless I’m experiencing situation with ur rss . Don’t know why Unable to subscribe to it. Is there anybody getting equivalent rss drawback? Anybody who is aware of kindly respond. Thnkx

I went over this website and I conceive you have a lot of great information, bookmarked (:.

What’s Happening i’m new to this, I stumbled upon this I have found It positively useful and it has helped me out loads. I hope to contribute & assist other users like its helped me. Good job.

This is really interesting, You’re a very skilled blogger. I have joined your rss feed and look forward to seeking more of your wonderful post. Also, I’ve shared your website in my social networks!

great issues altogether, you simply won a new reader. What may you suggest in regards to your publish that you made some days in the past? Any sure?

I will immediately snatch your rss feed as I can’t find your email subscription link or e-newsletter service. Do you have any? Kindly permit me understand in order that I may just subscribe. Thanks.

Some really interesting points you have written.Assisted me a lot, just what I was searching for : D.

Hola! I’ve been reading your weblog for some time now and finally got the courage to go ahead and give you a shout out from Atascocita Tx! Just wanted to mention keep up the excellent job!

I am continuously searching online for posts that can assist me. Thx!

I have been absent for a while, but now I remember why I used to love this site. Thank you, I will try and check back more frequently. How frequently you update your site?

local heating and air conditioning repair [url=https://otvetnow.ru]https://otvetnow.ru[/url] president of att

What i do not understood is actually how you’re not really much more well-liked than you may be right now. You are so intelligent. You realize therefore significantly relating to this subject, made me personally consider it from a lot of varied angles. Its like men and women aren’t fascinated unless it is one thing to do with Lady gaga! Your own stuffs excellent. Always maintain it up!

Today, I went to the beachfront with my kids. I found a sea shell and gave it to my 4 year old daughter and said “You can hear the ocean if you put this to your ear.” She put the shell to her ear and screamed. There was a hermit crab inside and it pinched her ear. She never wants to go back! LoL I know this is completely off topic but I had to tell someone!

I intended to post you a very little word in order to thank you very much once again for all the superb concepts you have featured on this site. It’s quite pretty open-handed of you to present freely what numerous people would’ve sold for an electronic book to help make some dough on their own, most notably seeing that you might have tried it in the event you decided. The good tips as well served to become great way to be certain that most people have the identical keenness like my own to grasp lots more pertaining to this issue. I know there are lots of more enjoyable times up front for individuals that look into your blog post.

8ay3i4

I do like the manner in which you have presented this difficulty and it really does give me personally a lot of fodder for consideration. However, from everything that I have seen, I basically trust when other reviews pack on that men and women stay on point and don’t start upon a soap box associated with some other news of the day. Anyway, thank you for this excellent point and though I do not really concur with this in totality, I respect your point of view.

g2lvfm

Hi there! This is my first visit to your blog! We are a collection of volunteers and starting a new project in a community in the same niche. Your blog provided us valuable information to work on. You have done a marvellous job!